如果要替AI時(shí)代的基礎(chǔ)設(shè)施寫一句註腳,大概會(huì)是:「算力不怕多,怕的是塞車。」當(dāng)GPU叢集橫向擴(kuò)張、節(jié)點(diǎn)數(shù)翻倍,資料中心的瓶頸不再只在 TOPS,而是節(jié)點(diǎn)之間能不能「不流汗地對(duì)話」。銅線在短距離內(nèi)堪用,但一旦速率衝上800G、1.6T甚至更高,電連結(jié)的損耗、熱與功耗就像三座小山,攔在系統(tǒng)擴(kuò)張的國(guó)道交流道口。

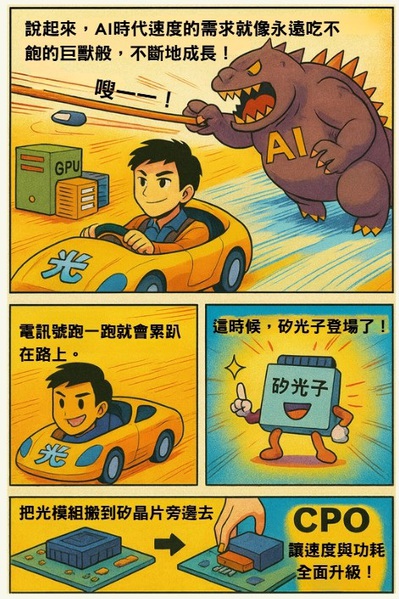

於是,光上場(chǎng)了—不是熟悉的可插拔模組那種「外掛型光」,而是把光直接搬進(jìn)晶片周邊甚至封裝內(nèi)部的「矽光子」與「近身光學(xué)」(CPO、Optical I/O)路線,準(zhǔn)備重寫連結(jié)的物理學(xué)設(shè)定檔。

技術(shù)圖譜:從可插拔到「近身光學(xué)」

矽光子不是新名詞,關(guān)鍵在於它把調(diào)變器、分光器、波導(dǎo)、檢測(cè)器等光學(xué)元件,與CMOS製程相容地整合在同一平臺(tái),讓光走入矽。典型元件組合包括:MZI或微環(huán)調(diào)變器(ring modulator)、鍺(Ge)光檢測(cè)器、矽波導(dǎo)與耦合器;雷射多半仍以III-V外掛或異質(zhì)整合方式供光。當(dāng)速率朝200G PAM4/λ前進(jìn)、通道數(shù)疊上去,整體功耗密度與I/O面積就是成敗分水嶺—也因此才有「把光靠近交換器或處理器」的CPO概念,以及更進(jìn)一步把光I/O做成晶粒(chiplet)與SoC串接的Optical I/O路線。

在供應(yīng)鏈層面,兩條平臺(tái)化路徑特別值得注意:其一是晶圓代工把SiPh納入標(biāo)準(zhǔn)工藝堆疊,提供設(shè)計(jì)套件與IP,如GlobalFoundries的Fotonix/45SPCLO,把RF/Analog與SiPh單晶片整合,縮短量產(chǎn)路徑;其二是IDM/生態(tài)系業(yè)者推出可重複使用的光I/O晶粒與外掛光源,主打低功耗、高頻寬、低延遲的「系統(tǒng)級(jí)I/O升級(jí)」。前者降低「造晶之痛」,後者則加快系統(tǒng)設(shè)計(jì)導(dǎo)入速度。

| 圖一 : 矽光子關(guān)鍵在於把調(diào)變器、分光器、波導(dǎo)、檢測(cè)器等光學(xué)元件,與CMOS製程相容地整合在同一平臺(tái),讓光走入矽。 |

|

應(yīng)用現(xiàn)況:AI叢集成為增長(zhǎng)引擎

AI訓(xùn)練叢集的網(wǎng)路側(cè)早已跨過(guò)800G,正走向1.6T與更高密度的背板/機(jī)櫃互連。無(wú)論是交換器ASIC還是GPU 直連,都面臨功耗牆與走線損耗的雙重壓力。因此,我們看到幾條「上量」跡象:其一,CPO被明確納入主流供應(yīng)商的產(chǎn)品規(guī)畫(huà)時(shí)間表;其二,Optical I/O 晶粒宣布支援UCIe等標(biāo)準(zhǔn)化介面,訴求讓SoC把銅I/O直接換成光I/O;其三,雲(yún)端與加速計(jì)算巨頭在公開(kāi)場(chǎng)合強(qiáng)調(diào)「光將成為下一代資料中心的必要條件」。當(dāng)路線圖從1.6T端口推進(jìn)到高達(dá)3.2T的封裝級(jí)光引擎時(shí),傳統(tǒng)可插拔的能效與機(jī)構(gòu)彈性就顯得吃力。

產(chǎn)業(yè)動(dòng)向亦在加速聚攏:NVIDIA於技術(shù)分享中強(qiáng)調(diào)微環(huán)調(diào)變器的高密度優(yōu)勢(shì),標(biāo)註以每波長(zhǎng)200Gbps PAM4為目標(biāo),並將CPO列為2026年前後世代系統(tǒng)的關(guān)鍵構(gòu)成;Ayar Labs等業(yè)者則推出 8 Tbps 等級(jí)的 UCIe光晶粒與16波長(zhǎng)共用光源,明示「把光當(dāng)成I/O」的系統(tǒng)級(jí)設(shè)計(jì)方法學(xué)。這些訊號(hào)與其說(shuō)是新品發(fā)布,不如說(shuō)是「設(shè)計(jì)規(guī)則」的變更通知:未來(lái)的叢集規(guī)模,離不開(kāi)矽光子的功耗與密度優(yōu)勢(shì)。

平臺(tái)與生態(tài):代工、IP與系統(tǒng)三方合奏

代工的角色在SiPh世代變得更接近「系統(tǒng)設(shè)計(jì)的放大器」。TSMC近年釋出包含光耦合、外掛光源接口與先進(jìn)封裝協(xié)同設(shè)計(jì)的藍(lán)圖(如 COUPE、生態(tài)計(jì)畫(huà)與iOIS架構(gòu)),意在把SiPh、CPO與先進(jìn)封裝(InFO/CoWoS/晶粒)串成一個(gè)可工規(guī)化的路徑;TrendForce亦指出TSMC在SEMICON展會(huì)上進(jìn)一步揭露CPO量產(chǎn)節(jié)點(diǎn),意味著「設(shè)計(jì)工具鏈+製程+封裝」的三位一體正在成形。GlobalFoundries則透過(guò)Fotonix強(qiáng)化「可量產(chǎn)的標(biāo)準(zhǔn)化光子製程」,輔以MPW與設(shè)計(jì)資源降低進(jìn)場(chǎng)門檻。

同時(shí),系統(tǒng)與GPU廠在生態(tài)戰(zhàn)上也沒(méi)有手軟。除了技術(shù)路線公開(kāi)化,我們看到並購(gòu)與投資加速:AMD收購(gòu)Enosemi補(bǔ)齊光子整合IP,並據(jù)報(bào)在臺(tái)灣建立矽光研發(fā)樞紐,這既是產(chǎn)品佈局,也是「人才與供應(yīng)鏈靠攏」的訊號(hào)。對(duì)於要在2026年後與NVIDIA同場(chǎng)競(jìng)速的玩家,光學(xué)互連顯然已是攻防必修學(xué)分。

商業(yè)化節(jié)奏:從先鋒部署到規(guī)模化

就時(shí)間軸來(lái)看,2024~2025年是示範(fàn)與早期部署階段:800G/1.6T連結(jié)開(kāi)始導(dǎo)入CPO與光I/O,先在高端交換器與AI訓(xùn)練叢集試點(diǎn);2026–2027年,隨製程成熟與成本曲線下滑,擴(kuò)大部署將推動(dòng)市場(chǎng)曲線轉(zhuǎn)折;更長(zhǎng)期(2030年前後),CPO與光I/O可能在部分場(chǎng)景取代高階可插拔光模組成為主流。各研究機(jī)構(gòu)對(duì)市場(chǎng)規(guī)模的預(yù)估有所差異,但共識(shí)是「高雙位數(shù)年複合成長(zhǎng)」以及北美資料中心率先放量。對(duì)硬體採(cǎi)購(gòu)決策者來(lái)說(shuō),這是一場(chǎng)「功耗/密度/可維護(hù)性」的多目標(biāo)優(yōu)化—而光學(xué)的能效優(yōu)勢(shì),會(huì)在機(jī)櫃密度與電費(fèi)上體現(xiàn)成實(shí)打?qū)嵉?TCO。

| 圖二 : CPO可讓電訊號(hào)的速度與功耗表現(xiàn)全面升級(jí)。 |

|

關(guān)鍵挑戰(zhàn):光與電的「雙棲婚姻」考題

1) 光源整合與耦合損耗。今天多數(shù)設(shè)計(jì)仍使用外掛或共用的III-V連續(xù)波光源(如SuperNova),如何在封裝距離內(nèi)把光高效率地送進(jìn)矽波導(dǎo)、並控制溫漂,是直接影響鏈路預(yù)算與良率的第一要?jiǎng)?wù)。異質(zhì)整合式雷射雖美好,但工藝與可靠度尚需時(shí)間沉澱。

2) 調(diào)變器密度與熱設(shè)計(jì)。微環(huán)調(diào)變器密度高、能效佳,但對(duì)溫度敏感;MZI穩(wěn)定度好、體積與功耗卻偏大。當(dāng)每波長(zhǎng)200G PAM4、通道數(shù)再倍增,封裝內(nèi)的熱場(chǎng)分佈與溫控策略(微型加熱器、校準(zhǔn)環(huán))就成為系統(tǒng)工程的重中之重。

3) 先進(jìn)封裝與測(cè)試。CPO/Optical I/O把「光」帶進(jìn)了OSAT的節(jié)拍:對(duì)準(zhǔn)精度、光學(xué)接口、晶粒堆疊與光纖管理都要求新的量測(cè)與自動(dòng)化流程。更關(guān)鍵的是「Known Good Die/Light」的定義與驗(yàn)證:如何在出貨前確保光晶粒與光源的長(zhǎng)期穩(wěn)定,是成本結(jié)構(gòu)的隱形變數(shù)。

4) 標(biāo)準(zhǔn)化與互通。UCIe/BoW等晶粒互連標(biāo)準(zhǔn)已逐漸成熟,但「光版UCIe」的實(shí)作細(xì)節(jié)(例如時(shí)脈恢復(fù)、誤碼率、鏈路訓(xùn)練、管理通道)仍在收斂中。沒(méi)有互通,就沒(méi)有真正的生態(tài)規(guī)模。

5) 成本與良率學(xué)習(xí)曲線。任何從「可插拔」轉(zhuǎn)向「封裝內(nèi)」的技術(shù),前期都會(huì)遇到成本躍升與產(chǎn)能可預(yù)測(cè)性問(wèn)題;唯有當(dāng)設(shè)計(jì)工具鏈、製程與測(cè)試三方形成正回饋,成本曲線才會(huì)按摩爾式的節(jié)奏滑落。從產(chǎn)業(yè)實(shí)務(wù)看,2026–2027年將是能否跨過(guò)「單位比特成本優(yōu)勢(shì)拐點(diǎn)」的決勝期。

策略建議:在不確定中把握確定性

對(duì)雲(yún)端服務(wù)商與大型企業(yè)使用者:短期可在高密度機(jī)櫃/交換器節(jié)點(diǎn)以「混合部署」方式試點(diǎn)CPO/Optical I/O,聚焦機(jī)櫃功耗、冷卻成本與線纜管理簡(jiǎn)化帶來(lái)的TCO實(shí)益;中期逐步導(dǎo)入支援光I/O的GPU/加速器平臺(tái),把光從機(jī)櫃邊緣推進(jìn)到封裝邊緣。

對(duì)晶片設(shè)計(jì)公司:及早把光I/O視為「架構(gòu)級(jí)元件」而非周邊,建立與代工/OSAT/光學(xué)供應(yīng)鏈的協(xié)同PDK與測(cè)試規(guī)格,並預(yù)留UCIe光域與管理通道的設(shè)計(jì)空間。當(dāng)AI叢集的網(wǎng)路/記憶體牆與冷卻牆同時(shí)逼近,能效與延遲將成為競(jìng)爭(zhēng)力比電晶體數(shù)更能說(shuō)服採(cǎi)購(gòu)的指標(biāo)。

對(duì)臺(tái)灣供應(yīng)鏈:TSMC的平臺(tái)化與本地科研人才密度,讓臺(tái)灣有機(jī)會(huì)在「SiPh+先進(jìn)封裝+晶粒生態(tài)」上扮演樞紐。無(wú)論是耦合結(jié)構(gòu)、光封裝治具、光纖/MT插針、或量測(cè)自動(dòng)化設(shè)備,都是可切入的利基點(diǎn)。近期國(guó)際大廠在臺(tái)布局矽光研發(fā),也是一記清楚的產(chǎn)業(yè)羅盤。

結(jié)語(yǔ):把「I/O」當(dāng)成產(chǎn)品力,而不只是規(guī)格

AI的算力曲線還會(huì)往上拱,但真正決定系統(tǒng)邊界的,越來(lái)越不是核心的FLOPS,而是邊緣的 I/O—能不能用更少的瓦數(shù)、在更短的距離內(nèi),搬運(yùn)更多的bit。矽光子與CPO/Optical I/O的價(jià)值,正在於把I/O從「被動(dòng)配角」變成「主動(dòng)架構(gòu)」。當(dāng)我們把光拉到晶片身邊,等於把系統(tǒng)的對(duì)話方式升級(jí)了一個(gè)層級(jí)。這不是「是否導(dǎo)入」的選擇題,而是「何時(shí)、在哪些節(jié)點(diǎn)先導(dǎo)入」的時(shí)間題。等到大家都換上光驅(qū)動(dòng)的語(yǔ)法時(shí),還在計(jì)較銅線的逗點(diǎn),就真的會(huì)慢半拍了。